DECODIFICADOR BCD/Hexa - 7 SEGMENTOS

Em muitos circuitos eletrônicos precisamos de uma interface humana pra rapidamente entendermos os dados que resultam de uma medição, de um ajuste ou comunicação. Um dos meios mais baratos e difundidos é a utilização de displays de leds com 7 segmentos. Com esses displays podemos facilmente apresentar todos os dígitos decimais (0 a 9) e algumas letras do alfabeto. Apesar de existirem displays mais completos, com mais segmentos ou mesmo de matriz de pontos, o de 7 segmentos ainda é o mais usado e de mais fácil utilização. Para isso, geralmente precisamos de um circuito auxiliar que faça a tradução dos dados digitais para que os displays acendam os segmentos corretos e possam assim mostrar o dígito correto.Esses circuitos são chamados de decodificadores BCD (binary coded decimal - decimal codificado em binário) para 7 segmentos. Para facilitar, esses circuitos são disponíveis em forma de circuitos integrados, sendo exemplos o CD4511 (CMOS) e os da série TTL 7446 7447 7448 (incluindo as variantes LS).

O problema desses cis é que eles só decodificam de 0 a 9 e às vezes queremos decodificar dígitos hexadecimais (acrescentando as letras A b C d E F). Antigamente existia um integrado de código DM9368 que era TTL e que fazia essa decodificação, mas hoje ele se tornou raro (difícil de encontrá-lo) e portanto deve ser caro pra comprar. Eu mesmo tenho umas 3 peças, mas vão virar peças de museu.

Aqui a tabela verdade do 9368, mostrando os dígitos headecimais:

Apesar de que hoje, quase não se usa mais circuitos integrados TTL ou CMOS das séries 74 e 4000/4500, pois praticamente quase tudo é implementado com microcontroladores, FPGA, PAL, etc, de vez em quando ainda precisamos de um decodificador desses.

Pra implementar um decodificador de BCD 7 segmentos, um circuito combinacional um pouco complexo é necessário. São várias portas lógicas interligadas e otimizadas com mapas de Karnaugh (cheguei a fazer vários exercícios de implementação desses decodificadores na escola, inclusive montando de verdade só com portas lógicas). Pra terem idéia, o diagrama de portas do 4511:

O 4511 além de tudo tem latches para manter os dados, mas ainda assim só consegue mostrar de 0 a 9.

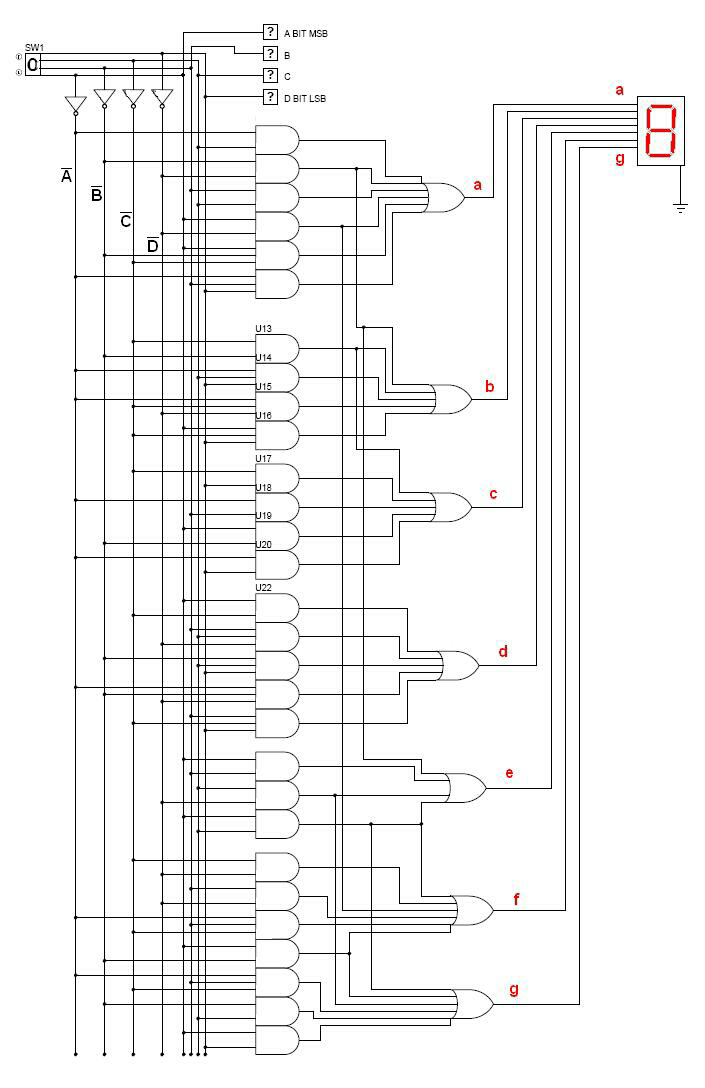

Se fosse implementar um decodificador hexadecimal, o circuito seria assim (sem otimização por mapas de Karnaugh):

Esse circuito usa muitas portas com várias entradas, além disso eu coloquei um recurso de poder usar tanto displays de catodo comum como de anodo comum, com as portas XOR (ou exclusivo) nas saídas, de forma a poder selecionar com uma entrada se a lógica seria positiva (catodo comum) ou negativa (anodo comum).

Aqui outro esquema otimizado com os mapas de Karnaugh:

Como não vale a pena usar PAL ou FPGA pra implementar isso, resta a opção de usar microcontroladores para realizar essa "glue logic". Microcontroladores simples com poucos pinos são muito utilizados para essas funções.

Infelizmente não achei nenhum PIC com a mesma pinagem de alimentação dos decoders comerciais, mas optei por um PIC de 14 pinos, o 16F630 (ou 16F676), que se não serve como substituto direto pino a pino para os decoders, pode simplificar bastante a falta de decoders hexadecimais:

Basta gravar o firmware abaixo, que o PIC se comporta como um decodificador hexadecimal para 7 segmentos, com a vantagem de que as saídas dele podem fornecer até 20mA de corrente para os segmentos de leds. Além disso implementei o recurso de modo de display (catodo comum ou anodo comum) que nenhum decoder comercial tem.

:100000000C288001840AFF3E031D01280728831362

:1000100003138312640008000730990083161F3011

:1000200085008701203084004030831201200F308A

:10003000B9000F300505B800640038083902031D07

:10004000222819283808B900051ABA14051EBA1052

:100050006400BA1C2D282F282E287028192838084B

:100060000F3C031C4D28362087004D2800308A00A5

:1000700038083D3E03188A0A82001F3403342D34A9

:100080002734333436343E3403343F3437343B344E

:100090003E341C342F343C34383438080F3C031CB5

:1000A0006F285820013903198512031D85166F2802

:1000B00000308A0038085F3E03188A0A8200013443

:1000C000003401340134003401340134013401348A

:1000D000013401340034013400340134013419286E

:1000E00038080F3C031C8E28772087008E280030AC

:1000F0008A0038087E3E03188A0A820020343C3485

:10010000123418340C34093401343C3400340834CB

:1001100004340134233410340334073438080F3CDA

:10012000031CB0289920013903198512031D851677

:10013000B02800308A003808A03E03188A0A8200DE

:10014000003401340034003401340034003400340D

:1001500000340034003401340034013400340034FD

:0601600019286300B1281C

:02400E00C43FAD

:00000001FF

A pinagem fica assim:

Mudando a entrada modo para nível baixo (0), o decodificador funciona com as saídas para displays de anodo comum, e a lógica invertida.

A seguir o firmware versão 16F676, que tem a mesma pinagem do 16F630, só que tem alguns recursos analógicos a mais (conversores A-D).

:100000000C288001840AFF3E031D01280728831362

:1000100003138312640008000730990083161F3011

:100020008500870191012030840040308312012037

:100030000F30B9000F300505B800640038083902E8

:10004000031D23281A283808B900051ABA14051EFA

:10005000BA106400BA1C2E2830282F2871281A28BC

:1000600038080F3C031C4E28372087004E280030EC

:100070008A0038083E3E03188A0A82001F3403347F

:100080002D342734333436343E3403343F3437345C

:100090003B343E341C342F343C34383438080F3C65

:1000A000031C70285920013903198512031D851678

:1000B000702800308A003808603E03188A0A8200DF

:1000C000013400340134013400340134013401348A

:1000D000013401340134003401340034013401347A

:1000E0001A2838080F3C031C8F28782087008F2897

:1000F00000308A0038087F3E03188A0A82002034C4

:100100003C34123418340C34093401343C34003497

:1001100008340434013423341034033407343808E9

:100120000F3C031CB1289A20013903198512031DC5

:100130008516B12800308A003808A13E03188A0AC3

:1001400082000034013400340034013400340034BF

:1001500000340034003400340134003401340034FD

:0801600000341A286300B228E4

:02400E00C43FAD

:00000001FF